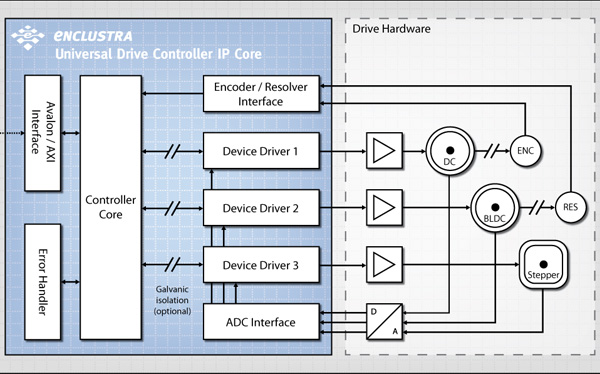

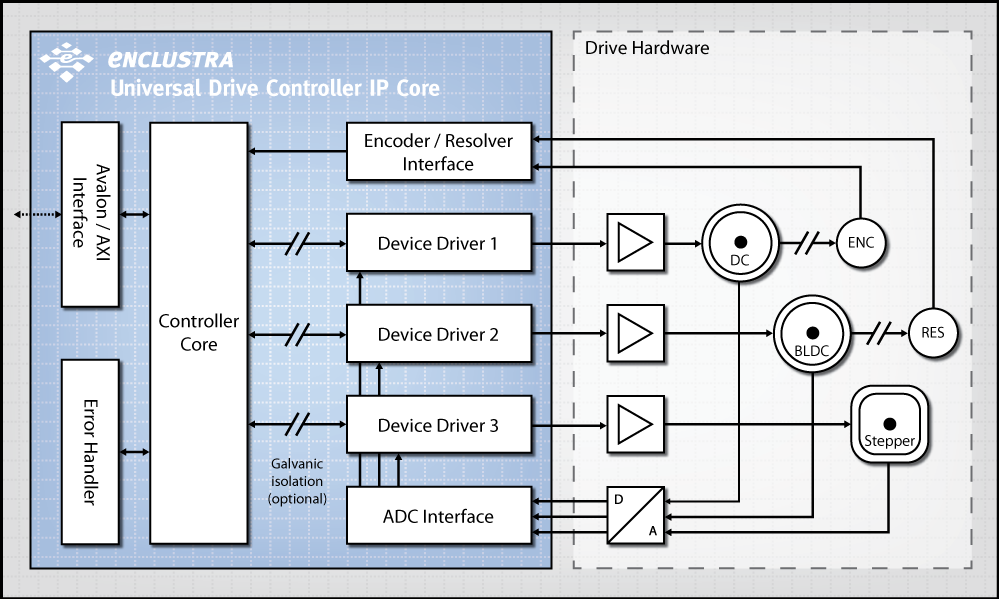

- 最大8軸ドライブコントローラ

- 最大最大200kHzの制御速度でドライブあたり4 PIDコントローラ(位置、速度、電流(S))

- 速度と加速度フィードフォワード

- 電圧、電流、温度スパーバイザ

- 高分解能PWM用に別のPWMクロック·ドメインベンダに依存しない実装

- アバロンやAMBA-AXIインタフェースで利用可能

- 3相ステッピングモータ(DC、BLDC、2)サポート

- エンコーダやレゾルバのサポート

- BLDCモータのフィールド指向制御(FOC)

- 完全に自律的なエラー処理

- 最低のソリューション全体のコストのために最適化

- 異なるデバイス間でADCシェアリングのサポート

FPGA IP - ユニバーサルドライブコントローラIPコア概要

Enclustra製ユニバーサルドライブコントローラIPコアは、既存または将来のFPGAデザインへの駆動制御機能を簡単に追加できるようになります。PCBスペースを消費し、不必要にプロジェクトBOMを延長する余分なドライブコントローラチップが不必要となります。将来のプロジェクトの駆動制御のニーズに対して、ユニバーサルドライブコントローラIPコアを利用選択するにより、大幅に市場投入までの時間を短縮するだけでなく、全体的なシステムになるコストダウンへとつながります。

FPGA IP - ユニバーサルドライブコントローラIPコア アーキチャ概要

FPGA IP - ユニバーサルドライブコントローラIPコア IPコア注文概要

| 基本コア① | ベースライセンス、2チャンネル、DCデバイスユニット |

| 基本コア② | ザイリンクスFGPA もしくは アルテラFGPA 選択 |

| オプション追加 | + シレスDC装置部 + 2相ステッピングモータ装置部 + 3相ステッピングモータ装置部 + 8チャネルのサポート + ガルバニック絶縁 + レゾルバインタフェース + マルチADCインターフェース(AD7266) |

基本コア①および②を選択をし、追加として、オプションを追加到います。お見積は別途お問い合わせください。

FPGA IP - UDP/IP Ethernet IPコア出荷物

| ユニバーサルドライブのIPコア |

+ ネットリスト(ソースコード引き渡し条件についてはお問い合わせください) + テストベンチ(VHDLソースコード) |

| ユニバーサルドライブAPI |

+ Cのオブジェクトファイルとヘッダファイル |

開発権は定義します。コピーおよび複製品は無制限です。