UAD2+ 通信ハードウェアユニバーサルアクセス装置

C166、XC166、XC2000、XE166、C166CBC、C166S V2、TriCore、PowerPC、PowerArchitecture、Cortex、ARM7、ARM9、ARM11、XScale、SuperH SH-2Aといったマイコンへのアクセスは、UAD2 +でサポートされています、ALL-IN-1の新しいアドオンインタフェースハードウェアユニバーサルデバッグエンジンのために。UAD2 +は、JTAG / OCDSを経由して、ターゲット·システム·アクセス·チャネルの多様な経由でのデバッグのための最先端のハードウェア·サポートを提供しています。これは、ホストPCとターゲットシステム上でUDE間の高速通信に最適化されています。UAD2 +が最適化された方法でUDEのすべてのアクセス機能をサポートしています。

C166、XC166、XC2000、XE166、C166CBC、C166S V2、TriCore、PowerPC、PowerArchitecture、Cortex、ARM7、ARM9、ARM11、XScale、SuperH SH-2Aといったマイコンへのアクセスは、UAD2 +でサポートされています、ALL-IN-1の新しいアドオンインタフェースハードウェアユニバーサルデバッグエンジンのために。UAD2 +は、JTAG / OCDSを経由して、ターゲット·システム·アクセス·チャネルの多様な経由でのデバッグのための最先端のハードウェア·サポートを提供しています。これは、ホストPCとターゲットシステム上でUDE間の高速通信に最適化されています。UAD2 +が最適化された方法でUDEのすべてのアクセス機能をサポートしています。

基本的な機能

- スタンドアロンの通信装置17 X 14 X 5cm USB 2.0を介してホストとの接続

- 最大480Mbpsの通信速度

- 低効率でサポートされているUSB 1.1

- 動作環境;Windows XP、Windows Vista、Windows 7、Windows8(32/64)

- 400Mbpsの通信速度

- 他IEEE1394Targetsとの最適な動作のための統合ハブ機能

- 動作環境;Windows XP、Windows Vista、Windows 7、Windows8(32/64)

- またはイーサネット経由

- 10/100Mbpsの通信速度

- 動作環境;Windows 2000、Windows XP、Windows Vista、Windows7、Windows8(32/64)

- ガルバニック絶縁標的インターフェイスはUAD2 +とターゲットとの間の電位差の悪影響を最小限にする

- 造でのJTAG延長テクノロジーが50センチメートル(1メートル。リクエストに応じてそれ以上)までUAD2 +とターゲットの間のJTAGケーブルの最大ケーブル長を備えています

- JTAGポートは、ドライバとケーブルを専用のポッドを介して提供されている

- シリアルワイヤデバッグ(SWD)のサポート

- シリアルワイヤビューワ(SWV)のサポート

- 計装トレースマクロセル(ITM)のサポート

- バスD-SUBオスコネクタ(CIAのピンアサインは)C167CR、C164CI、XC161CJ、XC164CS、XC167CIまたは同等のST10とのTriCoreへの通信チャネルのデバッグなどのシステムをターゲットにすることができCAN

- ISO-DIS 11898規格のオンボード高速CANバスインタフェースドライバ

- 可能なオンボードフラッシュプログラミングを経由してファームウェアの自動アップデート

- XC16x、C16x、ST10、ARM7、ARM9、およびのTriCoreターゲットシステムへの柔軟なシリアル高速通信。

以下のシリアルモードを使用できます。

| コントローラペリフェラル | インターフェース | 転送速度 | コネクタ | UDEサポート |

|---|---|---|---|---|

| ASC非同期 | RS232 | 最大1 Mbps | D-SUB9 | |

| ASCのA /同期 | RS485 | 最大1 Mbps | D-SUB9 | |

| ASC非同期 | TTL | 最大1 Mbps | 10ピン100milヘッダ | |

| SSCの同期 | RS485 | 最大1 Mbps | D-SUB9 | |

| SSCの同期 | TTL | 5 Mbpsのアップ | 10ピン100milヘッダ | |

| 3ピン·インターフェース(ソフトウェアSSC) | RS485 | 最大115 kbps | D-SUB9 | |

| 3ピン·インターフェース(ハードウェア) | TTL | 最大1 Mbps | 10ピン100milヘッダ | |

| (オンチップのCAN)CAN | CAN | 最大1 Mbps | D-SUB9 | |

| JTAG(インフィニオン) | LVTTL | 50 MHzまで | 16ピン100milヘッダ | |

| MiniJTAG(インフィニオン) | LVTTL | 30 MHzまで | ヘッダ基板対FTSH-105/FTSH-108 10/16-pin | |

| JTAG(ARM) | LVTTL | 30 MHzまで | 20ピン100milヘッダ | |

| JTAG(PowerPCのワンス) | LVTTL | 30 MHzまで | 14ピン100milヘッダ | |

| JTAG(パワーPC COP) | LVTTL | 30 MHzまで | 16ピン100milヘッダ | |

| JTAG(SuperH H-UDI) | LVTTL | 30 MHzまで | 14ピン100milヘッダー | |

| DAP(インフィニオン) | LVTTL | 50 MHzまで | 10ピンヘッダー対FTSH-105 | |

| MiniDAP / cJTAG(インフィニオン、PowerPC) | LVTTL | 50 MHzまで | 10ピン対TFM-105 | |

| SWD(ARM、Cortex) | LVTTL | 25 MHzまで | 10ピンヘッダー対FTSH-105 | |

| SWD(ARM, Cortex) | LVTTL | 25 MHzまで | 20ピン100milヘッダ | |

| OCDS L2(インフィニオン、オプション) | LVTTL | - | 60ピン対QTH-030から04 | |

| ETM Mictorコネクタ(ARM、オプション) | LVTTL | - | 38ピンAMPMODU | |

| ネクサスMictorコネクタ(PowerPC、オプション) | LVTTL | - | 38ピンAMPMODU |

コネクタのピンアサインの詳細については、ダウンロードエリアから入手可能な「UDEマニュアル付録」をご覧ください。

サポートされているマイクロコントローラ

- C166、ST10

- XC166、XC2000、XE166

- TriCore

- PowerPC、PowerArchitecture

- Cortex-A8、Cortex-M3、Cortex-R4

- ARM7、ARM、ARM11

- SuperH SH-2A

- XScale

ASCインタフェース

ユニバーサル·アクセス·デバイス2 +ターゲット·システムのアプリケーションとターゲット·システム·コントローラのASC0によって制御される外部のRS232デバイスとの間でバッファリングされた非同期通信パスを提供します。ASC-BSL/CAN、ASC-BSL/3PinまたはASC-BSL/SSCモードで、ASC0を介してターゲット·システム·コントローラを起動し、モニタコードを転送した後ASC0チャネルは、もはやデバッグ通信によって使用されず、したがって、アプリケーションの利用可能であるであろう。ユニバーサルアクセス装置2 +のバッファリングASC0で、アプリケーションの外部のRS232機器を手動で再接続する必要はありません- 。これは自動的にユニバーサルアクセス装置2 +によって行われますさらに、RS232経由でバッファリングされたASC0に、バッファなしのTTLレベルASC0がある利用できる。このために、ターゲット·システムに追加のハードウェア(RS232ドライバ)が必要とされない-の信号線のTxDとRxDに直接対応する制御端子に接続されています。

SSCのインタフェース

追加のハードウェアが必要とされないように、最大5Mbpsまでの最大伝送速度を達成することができる。

- ブートアップターゲットシステムをためRS232/ASC0。モニター(最大115kbpsでの<< 1秒)をダウンロードした後、RS232インタフェースは、アプリケーションで使用でき、外部のハードウェアやアプリケーションソフトウェアの再構成なしで、再び。

- 約ターゲットシステムRAMの3kByte SSCのモニタ用。

- 使用C16xコントローラの唯一の3ポート端子です。

- 実行時測定のための任意にタイマー。

3ピン·インターフェース

ASCブートストラップローダ/ 3ピンインタフェース-レスデバッグのための完璧なソリューションを監視し

、新しいASC-BSL/3Pinユニバーサルアクセス装置2 +、プラグアンドプレイのような、ターゲット·システムへのアクセスを実現することができるでサポートされている(ハードウェア)インターフェイスでは。念頭に置いて、システムリソースを節約し、このインターフェイスはRS232/ASC0およびROMを必要とせずにアップロード可能高速モニターの利点を維持し、ROMのプログラミング中、多くの場合、アプリケーション自体によって使用されている任意の他のコントローラの周辺機器を解放するために開発された前のデバッグターゲットシステムで。ターゲットシステムは、3ピンターゲット接続モニタと3ピン·インターフェースのための3行を追加ダウンロードするための標準的なRS232リンクを介してユニバーサルアクセス装置2 +に接続されている。

ASC-BSL/3Pinインターフェイスを使用すると、ホストとターゲットの通信速度 アップの12倍の速さで、標準的なホストのPC-COMxのベースRS232インターフェースよりはサポートされています。

- ブートアップターゲットシステムをためRS232/ASC0。モニター(最大115kbpsでの<< 1秒)をダウンロードした後、RS232インタフェースは、アプリケーションで使用でき、外部のハードウェアやアプリケーションソフトウェアの再構成なしで、再び。

- 約ターゲットシステムRAMの3kByte 3ピンモニター用。

- 使用C16xコントローラの唯一の3ポート端子です。

- 実行時測定のための任意にタイマー。

あなたの利点は: - 追加のモニターを必要としない追加のハードウェアがセットアップする必要がありません!

CANインタフェース

ユニバーサルアクセス装置2 +は、ホストPCとターゲットシステム間のCAN通信チャネルをサポートしています。

次のような利点が、それによって達成される。

- 通信チャネルが原因のアドレス指定CANバスノードのアプリケーションの作成およびデバッグに同時に使用することもできます。

- ターゲットシステムでのCANバスのデバッグ·モニタは、コードと128バイトのデータメモリのちょうど4キロバイトが必要です。それは容易にターゲットシステムのほぼすべてのタイプに統合することができる。4メッセージ識別子および2は、ホストとターゲットの通信のためのメッセージオブジェクトをCANモジュールを確保する必要があります。CANバスのタイミングはユーザー定義可能である。

CANデバッグインタフェースは、使用していますC167CR、C167CS、C164CI、C161CS、C161JS、XC161、XC164、XC167、ST10R167、ST10R168かのTriCore TC1775、TC1130のCANモジュール、内蔵TC1796 CAN誘導体または外部i82527 CAN通信用のバスコントローラホストPC上のデバッガ。コントローラエリアネットワーク(CAN)バスおよびその関連するプロトコルは、CANバスに接続されたステーションの数との間の非常に効率的な通信を可能にする。XC16x、C16x、ST10をベースのCANノードの数と複雑なシステムを設計する際に、同時にステーションの数にアクセスすることは非常に有利である。CANバスの他のソフトウェア性能強化機能は次のとおりです。CANバスのデバッグ·インタフェースは、常にソフトウェアの開発、テスト、およびオンサイトメンテナンスのため、ターゲットシステムへの迅速なアクセスを可能にする優れたソリューションです。

特別なCANバス·ターゲットモニタの特長

- XC16x、C16xターゲットシステムモニタは、オンチップの内部ST10は、モジュールと使用可能な外部i82527することができます。

- 標準評価ボード用のバスのROMモニタは、デバッガの標準パッケージに付属することができます。

- ユーザー固有のCANバスモニタはUDE-MONポータブルモニタパッケージから構成することができます。すべてのコンポーネント(ソース、オブジェクト、ライブラリ)が使用可能C16x / ST10クロスコンパイラと互換性があります。

- 標準および拡張識別子はサポートされています。

- CANモジュール内蔵を使用してモニターし、アプリケーション間で共有を中断することができます。

- CANバス(内部フラッシュや外部フラッシュ-EPROMは、AMD 29FのXXX)を介して、フラッシュ·プログラミング

- ROMレスのCANデバッグが可能(ASCブートストラップローダおよびCAN)を監視します。

CANバスアナライザ

- 独立した知的なサブシステムは、CANバスメッセージを連続的にトレースを可能にします

- 能力を観察するバスは、CANバスベースのデバッガ通信と組み合わせても使用することができるCAN

- テスト可能なアプリケーションのために理想的に適し - バス刺激することができます!

ユニバーサルアクセスデバイス2 + CANバスモニタツールは、CANバスを使用したアプリケーションのための開発援助として設計されており、完全に、CANアナライザを交換することになっていません。

JTAG

アイテムはオンボードデバッグサポート(OCDS) -インフィニオンC166CBC、C166S V2(XC16x)とユニバーサルアクセス装置2 +でユニバーサルデバッグエンジンでサポートされているのTriCoreファミリマイクロコントローラのための新しいデバッグインタフェースは、インフィニオン16のデバッグサポートの新技術を表して-と32 -ビットマイクロコントローラ。これまでのところ、OCDSの機能は、最新のC166CBC、C166S V2の誘導体および新世代32ビットμC-DSPのTriCoreアーキテクチャに実装されています。

ユニバーサルアクセス装置2 +のような本質的なOCDS機能のすべてをサポートしています。

- 標準の16ピン、インフィニオンのJTAG / OCDSのL1端子(2.5V - 3.3VのI / Oリング電圧)が50 MHzのシフトクロックにC166CBC、C166S V2およびのTriCore JTAGデバッグ通信チャネルをサポート - 3,5 Mバイト/ sまでの速度をダウンロードする

- 標準の20ピンARM JTAGコネクタ(2.5V - 3.3VのI / Oリング電圧)が25 MHzのシフトクロックにARM7/ARM9 JTAGデバッグ通信チャネルをサポート - 1 Mバイト/ sまで速度をダウンロードする

- コネクタ(2.5V - 3.3VのI / Oリング電圧)一度標準の14ピン·PowerPCは25 MHzのシフトクロックにデバッグ通信チャネルに一度、フリースケールのPowerPCをサポートしています

- 標準の16ピンのPowerPC COPコネクタ(2.5V - 3.3VのI / Oリング電圧)が25 MHzのシフトクロックに、IBM / Motorola社のPowerPC COPへのデバッグ通信チャネルをサポートしています

- JTAGインタフェースを介してホストデバッガの直接のターゲット·システム·アクセス(IEEE1149.1)

- アイテムはオンボードのデバッグ操作は、エミュレータのような追加のデバッグ機能をサポートしています

- ハードコードブレークポイント

- アクセスデータブレークポイントの読み取りまたは書き込み

- リアルタイム·トレースオペランドアクセス

これらのデバッグ機能を使用して、ターゲットシステムには追加のハードウェアまたはソフトウェアのリソースは必要ありません。そのため、マイクロコントローラの他のすべてのインターフェイスが制限なしでアプリケーションとシステムが使用可能なデバッガ、JTAG OCDS L1のポートを使用する場合には、その全生涯にわたるデバッグのための準備ができている。

JTAG OCDSユニバーサルデバッグエンジンと、L1(UDE)を用いてユニバーサル·アクセス·デバイス2 +は、次の主要な利点があります。

- ダウンロードのパフォーマンスを最大25倍高速 、低価格プリンタポートのソリューションよりも!劇的特に大規模なアプリケーション(1 + Mバイト)のデバッグセッションのターンアラウンドサイクルをスピードアップします。

- RAMまたはROMに必要なの常駐ターゲットモニタません。

- ROMまたはOnChip-Flash/OTPにプログラムコードをステップ実行するために利用可能なハードウェアブレークポイント。

さらに、複雑なトリガ条件を定義することができる。シンボリックトリガ条件は現在、強化された定義を備えています。ユニバーサルアクセス装置2 +で、シングルチップのアプリケーションは現在、高価なインサーキット·エミュレータなしで、JTAG OCDS L1を介してデバッグすることができます。

JTAG-エクステンダー

UAD2 +がデフォルトあたりのアクティブUAD-JTAGエクステンダーを搭載し、50センチメートル(1メートル。リクエストに応じてそれ以上)までUAD2 +とターゲットの間のJTAGケーブルの最大ケーブル長を可能にする。UAD-JTAG Extenderは、ドライバとケーブルを備えた専用のJTAGポッドを提供しています。サポートされているJTAGコネクタ:

- 16ピンシュラウドオスヘッダ - インフィニオンコネクタ

- 20ピンシュラウドオスヘッダ - のARMコネクタ

- ご要望に応じて、顧客のコネクタ

- ケーブル長さ50cm - ご要望に応じて、より長いケーブル長

- オープンドレインリセット#のサポート

- I / O操作に使用するターゲットMCUのI / O電圧

- 最高の性能とシグナル·インテグリティのためのLVDS(小振幅差動信号)技術。

OCDSのL2命令トレース

OCDSのL2トレースボードは、アドオンのユニバーサルアクセス装置2 +のためであり、リアルタイムでのTriCoreに、実行中のプログラムのトレース情報を記録することができます。

UAD OCDS L2トレースアドオンボード

システムは、最良の方法で、インフィニオンOCDS L2トレースポートの機能のすべての機能をサポートするために最適化されたソリューションです。

- 170 MHzまでサポートトレースポート

- 1Mサンプルトレースの深さ

- タイムスタンプの分解能は1 / f のCPU(つまり10nsのFの時のCPU = 100MHzの)

- 40ビットのタイムスタンプ範囲

- トレースユニットのトリガイベントを提供するための完全なOCDS L1機能をサポート

- 最適なトレースの利用のためのインテリジェントなトレースフィルタ

- のTriCoreとPCPトレース

- トレース制御と可視化のためのOCDSのL1トリガ信号の完全なサポート

- ペリフェラルや外部信号を観測するために追加の8外部トレースライン

- 外部コネクタポッドへのLVDSインタフェースは、60ピンOCDS L2高速コネクタ(インフィニオンが提案した)のためのポッドをサポートしています

- サポートされているデリバティブ:TC1130、TC1765、TC1796、TC1910、TC1912、TC1920

60ピンOCDS L2高速コネクタポッド

- のTriCore 1.3システム(TC11IB、TC1910、TC1912、TC1920と将来の誘導体)のOCDS L2ポートへの接続をサポートするために、インフィニオンはオススメしています

- SAMTEC 60ピン高速コネクタQSH-030-01-FDAに基づくコネクタシステム

- 150MHzのシステムクロックまでのシステムで使用する準備

- 3.6ボルトのTriCore 1.3 I / Oリング電圧2.5ボルトをサポートしています

- 高いトレース信号品質を確保するためにLVDSインタフェースを使用してベース基板をトレースする80ピンケーブル

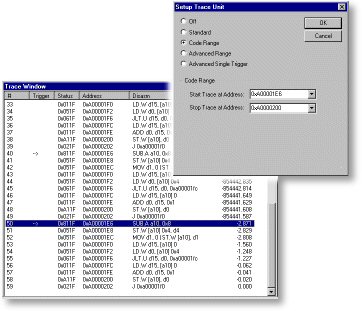

OCDS L2トレース機能のUDEをサポート

4セットアップモードによるトレース機能の完全な利用:

- 標準トレースタスクに簡単にアクセスできるようにする2標準モード

- トレースシステムの複雑な可能性へのフルアクセスを可能にするために2エキスパートモード

- ソースコードのシンボリック参照のトレース設定の完全な接続

- 内部および外部トレース·イベントの可視化

- トレース出力およびC言語ソース間のブラウズ機能

ARM7およびARM9のためのETMおよびETBトレース

ARM7およびARM9 ETMトレースボードは、アドオンのユニバーサルアクセス装置2 +のためであり、リアルタイムでのARMデリバティブの実行中のプログラムのトレース情報を記録することができます。

UAD ARM7およびARM9 ETMトレースアドオンボード

システムは、最良の方法でのARM ETMトレースポート機能のすべての機能をサポートするために最適化されたソリューションです。

- 170 MHzまでサポートされているポートをトレース、4または8ビット幅

- ハーフレートクロック·モードがサポート

- 1Mサンプルトレースの深さ

- タイムスタンプの分解能は1 / f のCPU(つまり10nsのFの時のCPU = 100MHzの)

- 40ビットのタイムスタンプ範囲

- トレースユニットのトリガイベントを提供するための完全なETM機能をサポート

- 最適なトレースの利用のためのインテリジェントなトレースフィルタ

- ペリフェラルや外部信号を観測するために追加の8外部トレースライン

- 外部コネクタポッドへのLVDSインタフェースは、38ピンETM Mictorコネクタ高速コネクタ(ARMが提案された)のためのポッドをサポートしています

- サポートされているデリバティブ:LPC21xx、AT91RM9200

38ピンのARM7およびARM9 Mictorコネクタ高速コネクタポッド

- ETMをARMに接続をサポートするために、ARMはオススメしています

- Mictorコネクタ38ピン高速コネクタをベースコネクタシステム

- 170MHzのシステムクロックまでのシステムで使用する準備

- 3.6ボルトのI / Oリング電圧2.5ボルトをサポートしています

- 高いトレース信号品質を確保するためにLVDSインタフェースを使用してベース基板をトレースする80ピンケーブル

ETMトレース機能のUDEをサポート

セットアップモードによるトレース機能の完全な利用:

- 標準トレースタスクに簡単にアクセスできるようにする1標準モード

- ソースコードのシンボリック参照のトレース設定の完全な接続

- 内部および外部トレース·イベントの可視化

- トレース出力およびC言語ソース間のブラウズ機能

ETBトレース機能のUDEをサポート

エンベデッドトレースバッファ(ETB)が埋め込まれたオンチップの円形のトレース·バッファにより、ARM誘導体のETMユニットを拡張します。高速トレースシグナリングは外部ユニットに転送する必要がないので、これは外部トレースユニットの適応を簡素化します。トレースバッファは、JTAG通信チャネルを介して管理され、読み出される。

- サポートされているデリバティブ:LPC3000誘導体

PowerArchitecture用ネクサストレース

ネクサス2ビットの最大1メガサンプルを記録することができる、4ビットまたは、MPC55xxファミリーのMCUを、最大180 MHzのクロック周波数であっても12ビット幅のトレースデータポートは、支持されている。

UADネクサストレースアドオンボード

システムは、最良の方法で、ネクサストレースポートの機能のすべての機能をサポートするために最適化されたソリューションです。

- 180 MHzまでサポートされているポートを追跡、2、4、または12ビット幅

- ハーフレートクロック·モードがサポート

- 1Mサンプルトレースの深さ

- タイムスタンプの分解能は1 / f のCPU(つまり10nsのFの時のCPU = 100MHzの)

- 40ビットのタイムスタンプ範囲

- トレースユニットのトリガイベントを提供するためのネクサス機能をサポート

- 最適なトレースの利用のためのインテリジェントなトレースフィルタ

- ペリフェラルや外部信号を観測するために追加の8外部トレースライン

- 外部コネクタポッドへのLVDSインタフェースは、38ピンネクサスMictorコネクタ高速コネクタ用のポッドをサポートしています

- サポートされているデリバティブ:MPC55xx、MPC56xx、SPC56xx誘導体

38ピンネクサスMictorコネクタ高速コネクタポッド

- ネクサストレースを介した接続をサポートするために、ネクサスはオススメしています

- Mictorコネクタ38ピン高速コネクタをベースコネクタシステム

- 180MHzのシステムクロックまでのシステムで使用する準備

- 3.6ボルトのI / Oリング電圧2.5ボルトをサポートしています

- 高いトレース信号品質を確保するためにLVDSインタフェースを使用してベース基板をトレースする80ピンケーブル

インフィニオンのTriCoreとXC2000のためのDAPサポート

デバイスは、アクセスポートのDAP、新しいデバッグ·インタフェースは、AUDO未来インフィニオン、によって設立された

XC2000M、XE166Mデバイスやその他の今後の16ビットおよび32ビットのマイクロコントローラ·。2線式または3線式の

DAPは、JTAGベースの通信チャネルを既存より高い伝送速度を有するデバッグ通信を可能にする。新しいボードコネクタは0.05インチの複列10ピンのマイクロ端子ターゲットシステム側基板スペースを節約したシュラウドを、キーイングである。

DAP用のUDEをサポート

DAPを介して高速ダウンロードは、通信装置UAD2とUAD2 +、ユニバーサルデバッグエンジンのハードウエアのアドオンにより達成される。

- 50 MHzの@ DAP通信周波数

- (TC1797 AUDO未来で)3,5 Mバイト/秒までの転送速度

- 2-wire/pinと3-wire/pin DAPモードサポート

- single-wire/pin DAPモード用に準備

- 示す電力用LED

LVDSとUAD DAPエクステンダー

DAP延長剤とUAD2 +が最も高いため、LVDS技術と電気的に絶縁インタフェースを使用して

、パフォーマンスとDAPインタフェースのシグナル·インテグリティ。これは、最大2メートルのインターフェースケーブルの長さを可能にする。

Cortex用SWDサポート

シリアルワイヤデバッグ(SWD)インタフェースまたはシリアルワイヤデバッグポート(SW-DP)は、デバッグおよびトレース技術、ARM CoreSightの©の特徴の一つである。SWDの最初の実装は、発光体のマイクロのCortex-M3コアのStellaris(現テキサス·インスツルメンツ)の誘導体およびSTマイクロエレクトロニクスSTM32ファミリの誘導体で実現される。既知のJTAGデバッグポート(JTAG-DP)は、さらにサポートされています。デバッグポート、SWD、代替JTAGデバッグ·ポートは、シリアルワイヤJTAGデバッグポート(SWJ-DP)、CoreSightの標準ポートに組み合わせることができます両方。SWDを使用する場合、TDO信号は、シリアルワイヤ出力を介してトレースイベントメッセージを提供することができます(SWO)。この動作は、単一のピンを介して出力システムイベントにシリアルワイヤビューワ(SWV)で使用することができます。

- 計装トレースITM(printf関数に似たデバッグ)

- ウォッチポイントトレースDWT、命令ポインタトレース

- イベントトレース(割り込み)

SWD用UDEサポート

SWD経由でターゲット接続が通信機器UAD2とUAD2 +、ユニバーサルデバッグエンジンのハードウェアアドオンと追加UAD2 SWDアダプタによって達成される。

LVDSとUAD SWDエクステンダー

エクステンダーとSWDアダプタに交渉UAD2 +が最高のパフォーマンスとSWDインタフェースのシグナル·インテグリティのためのLVDS(小振幅差動信号)技術と電気的に絶縁インターフェースを使用しています。これは、最大2メートルのインターフェースケーブルの長さを可能にする。

静電気の注意事項

!静電放電(ESD)に敏感な電子部品を損傷する可能性が万ボルト(10 kVの)上のいくつかのケースでは-いくつかの条件の下ではアクセスデバイスとユーザのターゲット·ハードウェアとの間の静電気と接地電位の違いは高電圧を構築することができます。このビルドアップ電圧、高速、高電流波形と高速磁気(Hフィールド)での結果や静電(電界)の外乱の静電気放電。電子部品や回路に放電が失敗、その結果、ハードウェア·コンポーネントに損傷を与えたり、破壊することができますおよび信頼性を低減。なぜなら非ホットプラグ対応3.3ボルト/ 5ボルトの- JTAGおよび3Pin/SerialコネクタのTTLプロパティは、これらのポートは、特に絶滅の危機に瀕している。これらのピンの最大電圧を超えないことが5.5ボルト。特にグランドプレーンを最初に接続されていない場合は、UADの地面に静電気と接地電位の放電による損傷からハードウェアを保護するには、いくつかの基本的な注意事項に従っている必要があります。

- あなたがアクセスデバイスからのケーブル接続を変更する前に、アクセス·デバイスとターゲット·システムから電源を取り外してください。

- アクセスデバイス、ホストPCとターゲットハードウェアとの間の静電気とグランド電位がバランスしていることを確認してください。高電位差の危険がある場合は、低抵抗接続を介して同一のグランドドメインにアクセス装置は、ホストPCとターゲットハードウェアを接続する必要があります。

- システム上のターゲット接続とパワーを確立します。

すべての場合において、次のルールが出席しなければなりません。デバイス間の最初の接続は、グラウンドを介して行われなければならない!ソリューションのすべてのユニバーサル·アクセス·デバイスは、前面側のグランドソケットが装備されている。静電気を放電し、ユニバーサル·アクセス·デバイス、ホストPCとターゲット·ハードウェア間のグランド電位のバランスをとるため、このグランド·ソケットを使用してくださいする前に あなたがアクセスデバイスにターゲットハードウェアを接続してください。UAD2 +が既に保護機能が含まれています。これらの保護機能があることを、予めご了承ください ません、上記の注意事項を中断します。

商標:TriCoreは、インフィニオンテクノロジーズの商標です。ARM、EmbeddedICEの親指は、ARM Limitedの登録商標です。ARM7、ARM9、組込みトレースマクロセルおよび組み込みトレース·バッファは、ARM Limitedの商標です。FireWireはアップルコンピュータ社の商標です。たi.Linkはソニー株式会社の商標です。STは、STマイクロエレクトロニクスグループに属する会社の登録商標です。XScaleのは、STマイクロエレクトロニクスグループに属する会社の登録商標です。その他のブランドあるいは製品名は全て、それぞれのホールダーの所有物です。