- 完全な1Gbit/secワイヤスピードで動作

- IPv4およびイーサネットレイヤ処理

- ヘッダパススルーモード

- 選択的に送信データストリームに埋め込まれた値で初期UDP /IP/ETHヘッダーフィールド値をオーバーライド

- ユーザアプリケーションに容易に送達するための受信データストリーム内の選択的に埋め込むUDP / IP / ETHヘッダーフィールド値

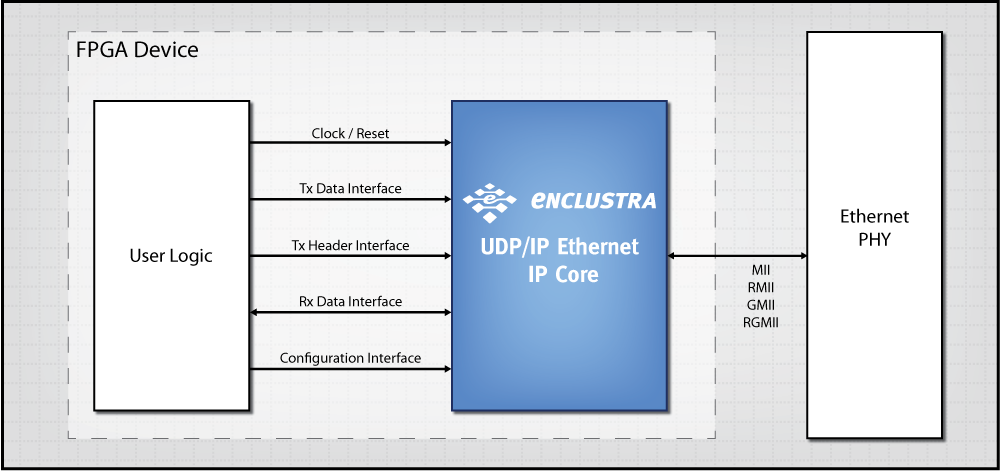

FPGA IP - UDP/IP Ethernet IPコア概要

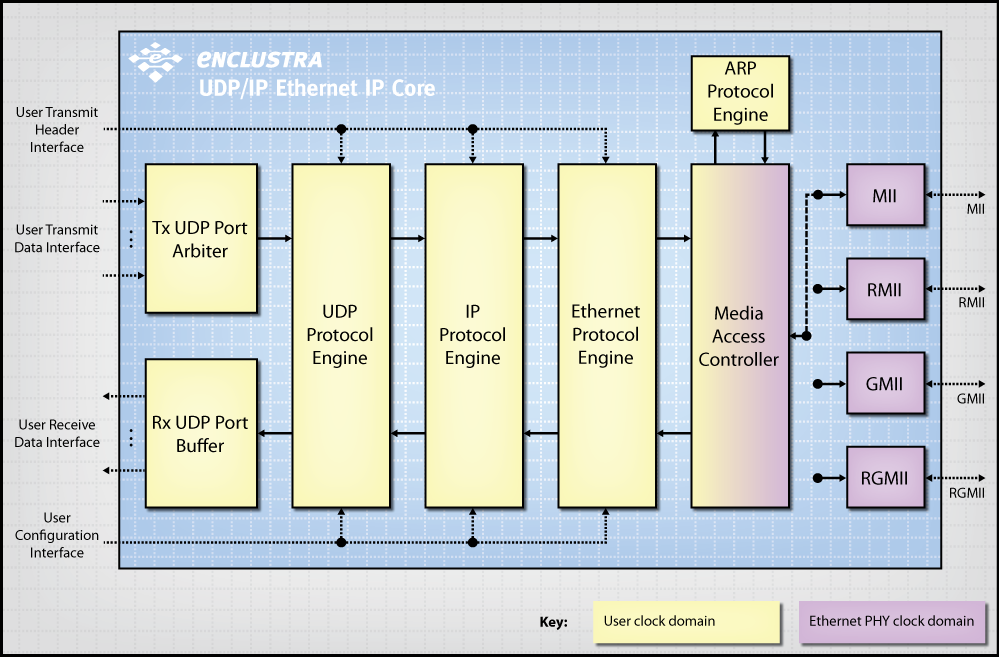

Enclustra製UDP / IPイーサネットIPコアは、簡単にUDPプロトコルを使用して、イーサネットを介して他のサブシステムと通信するためにFPGAベースのサブシステムを可能にします。IPコアは、現在、アルテラとザイリンクスのFPGAアーキテクチャで使用するための高度な設定と最適に実装されています。これは、ユーザ·ロジックへのインタフェースを使用して簡単に提供し、一般的なメディア独立インターフェースMII、RMII、GMIIおよびRGMIIをサポートしています。125MHzで動作、8ビット幅の送信および受信インターフェース可能なIPコアは、完全な1GB/sのワイヤスピードで動作することができます。また、100MB/sと10MB/sの動作もサポートされています。

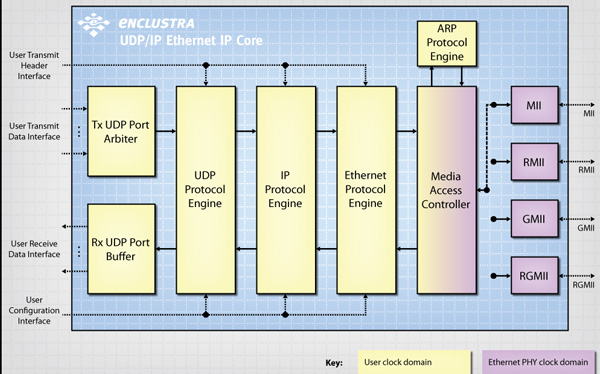

FPGA IP - UDP/IP Ethernet IPコア アーキチャ概要

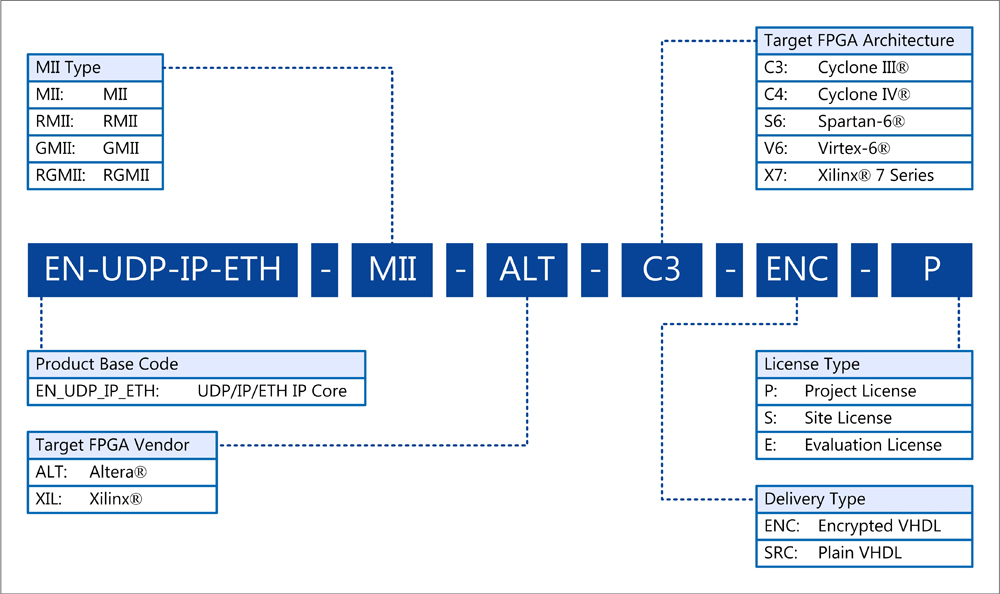

FPGA IP - UDP/IP Ethernet IPコア注文概要

FPGA IP - UDP/IP Ethernet IPコア出荷物

+ UDP / IP、イーサネットIPコア

++ VHDLソースファイル(プレーンまたは暗号化された、製品のオプションによって異なります)

++ プリコンパイル済みのModelSim®シミュレーションライブラリ

++ ユーザーマニュアル(PDFダウンロード)

+ UDP / IPイーサネットIPコアのリファレンスデザイン

++ リファレンスデザインのトップレベルのVHDLファイル(プレーンVHDL)

++ UCF / XDC / SDC制約ファイル(製品オプションによって異なります)

++ ザイリンクスISE®/ザイリンクスVivado™/アルテラのQuartus®®IIプロジェクトファイル(製品オプションによって異なります)

++ トップレベルのシミュレーションテストベンチファイル(プレーンVHDL)

++ トップレベルのシミュレーションModelSimのプロジェクトファイル

++ ドキュメンテーション(UDP / IP / ETH IPコアユーザーマニュアルに統合)